# **UM-SJTU** Joint Institute

## Ve270 Introduction to Logic Design

by Xia Fangzhou 5113709225 Xue Jiong 5113709218

2013.7.23

Design of a Digital Device

# \*交大密西根学院\*

### **Objectives**

In this lab, we are asked to design a digital device which integrates the function of a character roller and a simple calculator. The user should be able to switch between these two functions by toggling a switch on the FPGA board.

#### **Problem Definition**

In this lab, we are asked to integrate all the components we have used to design a digital device which has the function of a roller and a simple calculator which can add two 4-bit 2's complement numbers.

The character roller designed in this lab should be able to roll the student ID over four SSDs automatically which is suitable for human eyes. The rolling should start automatically once the controlling switch is turned up.

The 4-bit 2's complement number simple calculator should be able to add the next four bits input to the four bit number stored in the FPGA when an equal button is pressed. Over flow should be indicated using a LED if detected. The initial value of the calculator should be set to zero when the controlling switch is turned down.

As a whole, the digital device designed in this lab should have five switches, one equal button for input and four SSDs, one LED for output.

#### **System Partitioning**

Due to the complexity of the device, we use Verilog HDL to describe the behavior of the circuit. Things become relatively easy in this way since we just need to specify the system input and output and the timing issues of the circuit. As for system partitioning, we divide the system into the following parts:

Clock Dividers: Two clock divider for character rolling and SSD displaying.

SSD Displayer: To display the number on four SSD according to the input.

SSD Driver: Generate the signal to control the character position displayed on the SSD driver.

Character Roller: Predefined character shifter.

Adder: Simple calculator which adds the value of the 2's complement numbers.

Debouncer: Optional part to stabilize the button.

## 一•交大密西根学院•

**UM-SJTU** Joint Institute

#### **Design Entry**

Based on the system partition, we describe the behavior of the circuit directly using Verilog HDL. The Verilog HDL code goes as the following.

```

Tue Jul 23 20:57:31 2013

ForReportOnly.v

1

'timescale 1ns / 1ps

module Lab8(reset, control, equal button, clock, operand, ssd driver, ssd shine,

3

overFlowIndicator);

input reset;

input equal button;

6

input control;

input clock;

input [3:0] operand;

8

9

output [6:0] ssd_driver ;

10

output [3:0] ssd shine ;

11

output overFlowIndicator;

12

wire second0;

13

wire display;

14

wire reset :

15

wire equal;

wire control ;

17

wire clock:

1.8

wire [3:0] ssd_shine;

19

wire [6:0] ssd driver ;

wire [3:0] operand;

20

21

wire ssd clock;

wire [15:0] ssd feed signal;

23

wire overFlowTester;

24

reg [3:0] displayInfo [3:0];

25

reg [3:0] numericalResult;

reg [3:0] nextNumericalResult;

26

27

reg [3:0] signIndicator;

28

reg overFlowIndicator;

reg [25:0] div0;

29

30

reg [10:0] divd;

reg [51:0] studentID;

31

reg [3:0] temp;

32

reg [3:0] absoluteValue;

reg [24:0] equal_count;

34

35

37

assign second0 = (div0==26'd2000 0000);

assign equal = (equal count==25'd50000);

38

assign ssd clock = display;

assign ssd_feed_signal = {displayInfo[3],displayInfo[2],displayInfo[1],displayInfo

assign overFlowTester = ((nextNumericalResult[3]^numericalResult[3]) && (numericalResult[3])

40

41

[3] == operand[3])) ? 1:0;

ssdRollerModule ssdDisplay(reset,ssd_clock,ssd_feed_signal,ssd_shine,ssd_driver);

42

43

//equal debounce

45

always @ (posedge clock, posedge reset, posedge equal)

46

begin: equalDebounce

if(reset==1'b1) equal count<=25'd0;

else begin

48

49

if(equal==1'b1)

50

begin

51

if (equal_button==1'b0) equal_count<=25'd0;</pre>

52

else;

53

end

5.4

else begin

55

if(equal button==1'b1) equal count<= equal count+25'd1;</pre>

else equal_count<=25'd0;

56

57

Page 1

```

## 一•交大密西根学院•

# Shanghai Jiao Tong University

#### **UM-SJTU** Joint Institute

Tue Jul 23 20:57:32 2013 ForReportOnly.v end 59 end 60 61 62 //clock divider0 63 always @ (posedge clock, posedge reset,posedge second0) begin: clock0 if(reset==1'b1) div0<=26'd0; 65 66 else begin 67 if(second0==1'b1) div0<=26'd0; 68 else 69 div0 <= div0+26'd1; 70 end 71 end 72 //display clock divider 73 74 always @ (posedge clock, posedge reset, posedge display) 75 begin: SSDdisplay 76 if(reset==1'b1) divd<=11'd0; 77 else begin 78 if (display) divd<=11'd0; 79 else 80 divd <= divd+11'd0001; 81 end 82 end 83 84 //roller 85 always @ (posedge second0, posedge reset) 86 begin : roller if (reset == 1'b1) begin studentID<={4'b1110,4'b1110,4'b1110,4'b1110,4'd5,4'b1,4'd1,4'd3,4'd7,4'd0,4'd 8.8 4'd2,4'd5}; 89 temp<=4'b1110; 90 end 91 else begin if (control ==1'b1) 92 93 begin 94 studentID[51:4] <= studentID[47:0]; studentID[3:0] <= temp[3:0]; 95 96 temp[3:0] <= studentID[51:48]; 97 end 98 else; end 99 100 end 101 102 //adder 103 always @ (posedge equal, posedge reset) begin : adder if (reset == 1'b1) begin 105 106 overFlowIndicator<=1'b0; 107 numericalResult<=4'b0000; 108 signIndicator<=4'b1111; end else begin 110 111 if (control ==1'b0) 112 begin 113 overFlowIndicator<=overFlowTester; numericalResult<=nextNumericalResult; if (nextNumericalResult[3]==1'b1) 115 Page 2

172

173

ssd selection<=4'b1110;

input\_4\_bits<=ssd\_signal[0];

## -•交大密西根学院•

#### **UM-SJTU** Joint Institute

Tue Jul 23 20:57:32 2013 ForReportOnly.v 116 begin 117 signIndicator<=4'b1110; 118 absoluteValue<=(~nextNumericalResult)+1; 119 120 else if (nextNumericalResult[3]==1'b0) 121 hegin 122 signIndicator<=4'b1111; 123 absoluteValue<=nextNumericalResult; 124 end 125 end 126 else signIndicator<=4'b1111;</pre> 127 end 128 end 129 // Display Control 130 131 always @ (posedge clock) 132 begin: displayControl 133 nextNumericalResult<=numericalResult+operand; 134 if(control==1'b1) begin 135 displayInfo[3]<=studentID[51:48]; 136 displayInfo[2] <= studentID[47:44]; 137 displayInfo[1] <= studentID[43:40]; 138 displayInfo[0] <= studentID[39:36]; 139 140 else if(control==1'b0) begin 141 displayInfo[3]<=4'b1111; displayInfo[2]<=4'b1111; 142 143 displayInfo[1] <= signIndicator; 144 if(absoluteValue==4'b1000) displayInfo[0]<=absoluteValue;</pre> 145 else displayInfo[0]<={1'b0,absoluteValue[2:0]};</pre> 146 end 147 else; 148 end 149 endmodule 150 //ssd Controller 151 module ssdRollerModule(reset\_signal,clock\_signal,input\_desplay\_signal,ssd\_selection) output\_7\_bits ); 153 parameter n=4; 154 input clock signal; 155 input reset\_signal; input [n\*4-1:0] input desplay signal; 156 157 wire [3:0] ssd\_signal [n-1:0]; 158 output [6:0] output\_7\_bits; 159 output [n-1:0] ssd\_selection; reg [3:0] input\_4\_bits;

reg [6:0] output\_7\_bits; 160 161 162 reg [n-1:0] ssd selection; 163 164 assign {ssd\_signal[3],ssd\_signal[2],ssd\_signal[1],ssd\_signal[0]}=input\_desplay\_signal[3] 165 always @ (posedge clock signal, posedge reset signal) 166 167 if (reset\_signal) ssd\_selection<=4'b0111;</pre> 168 else begin 169 case (ssd selection) 170 4'b0111: 171 begin

1

Page 3

## 一,交大密西根学院,

#### **UM-SITU** Joint Institute

Shanghai Jiao Tong University

```

Tue Jul 23 20:57:32 2013

ForReportOnly.v

174

end

175

4'b1110:

176

begin

ssd_selection<=4'b1101;

177

178

input 4 bits<=ssd signal[1];

179

end

180

4'b1101:

begin

ssd_selection<=4'b1011;

182

183

input_4_bits<=ssd_signal[2];

184

end

4'b1011:

185

begin

187

ssd selection <= 4'b0111;

188

input 4 bits<=ssd signal[3];

189

end

default ssd selection<=4'b0111;

190

191

endcase

192

end

193

always @(input_4_bits,ssd_selection)

begin: SSDCASE

195

196

case (input 4 bits)

197

4'b0000: output_7_bits <= 7'b0000001; //0

198

4'b0001: output_7_bits <= 7'b1001111; //1

4'b0010: output_7_bits <= 7'b0010010; //2

4'b0011: output_7_bits <= 7'b0000110; //3

200

4'b0100: output_7_bits <= 7'b1001100; //4

201

4'b0101: output_7_bits <= 7'b0100100; //5

4'b0110: output_7_bits <= 7'b0100000; //6

202

203

4'b0111: output 7 bits <= 7'b0001111; //7

4'b1000: output_7_bits <= 7'b00000000; //8

4'b1001: output_7_bits <= 7'b0000100; //9

205

206

207

4'b1010: output_7_bits <= 7'b0001000; //A

4'b1011: output_7_bits <= 7'b1100000; //b

208

4'b1100: output 7 bits <= 7'b0110001; //C

4'b1101: output 7 bits <= 7'b1000010; //d

209

210

4'b1110: output_7_bits <= 7'b11111110; //-

211

4'b1111: output 7_bits <= 7'b11111111; //nothing default: output 7_bits <= 7'b11111111;

212

213

endcase

215

end

216

endmodule

```

Page 4

#### **Test Plan**

In order to test the design, generate the RTL and check if all the necessary components have been implemented based on the Verilog code.

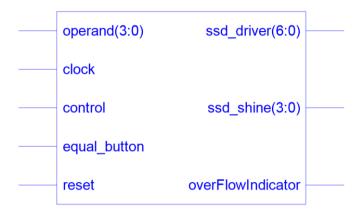

Figure 1 Block Diagram of the Designed Digital Device

Figure 2 Generated RTL Schematic

## ——·交大密西根学院·

#### **Simulation Results**

Due to the complexity of the design, it is not reasonable to simulate the entire circuit using test bench wave form. Since we integrated all the previous working components except for the adder to design this digital device, simulations for the individual components are not necessary.

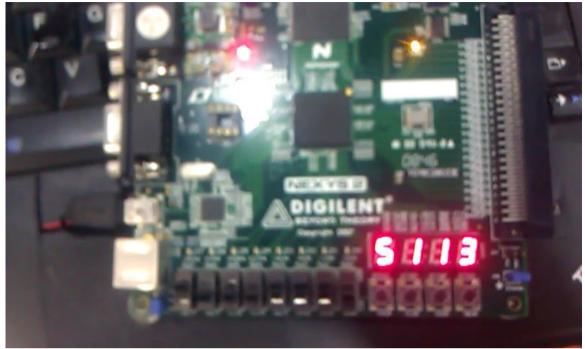

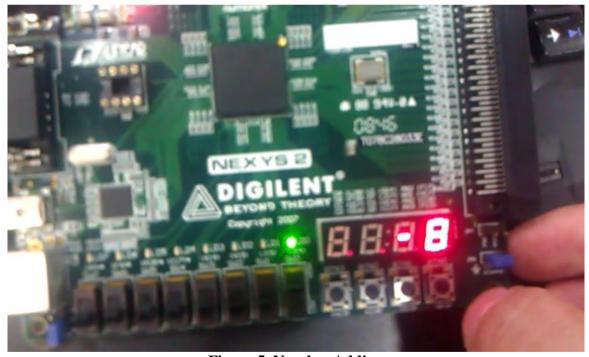

#### **Hardware Implementation and Testing**

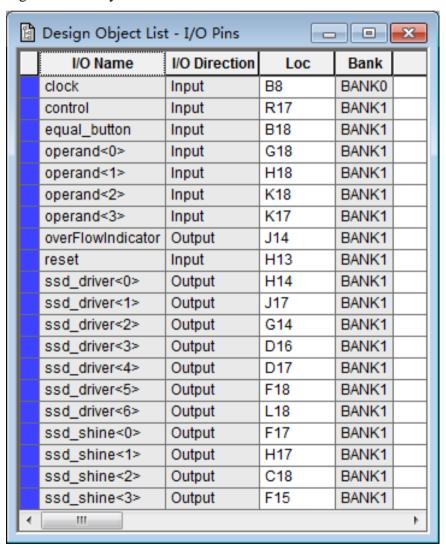

To test our design, we used the XC3S1200E FPGA board and assign the corresponding IO pins on the board. We demonstrated the functionality of our driver design to the TAs during lab. For the additional debouncing functionality, we demonstrated by comparing the effect with no debuncing version of the design and actually noticed the difference.

Figure 3 Assignment for IO Pins

## 一·交大密西根学院•

**UM-SJTU** Joint Institute

Figure 4 Character Rolling

Figure 5 Number Adding

#### **Conclusions**

In this lab, we managed to design a relatively complicated digital system. This experience is very useful since it is the first time for us to combine different module designed before to accomplish a complicated design. This lab greatly cultivated our ability to describe the behavior of the circuit using Verilog, which is indeed a powerful tool.